AMD doubles the size of their per core L3 Cache in Zen 2 “Rome” processors

AMD doubles the size of their per core L3 Cache in Zen 2 “Rome” processors

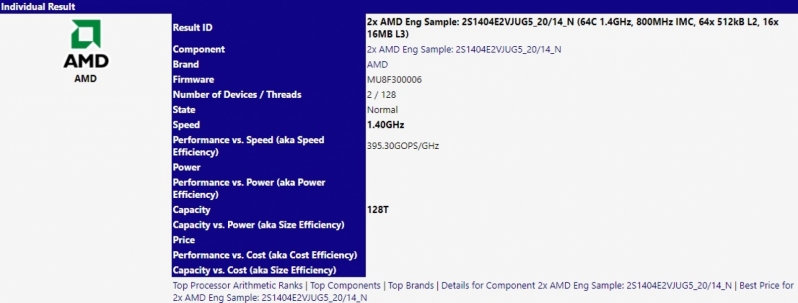

When comparing the results from AMD’s latest engineering sample (link) to an equivalent result from a dual-socket EPYC 7601 setup (link), we can see two things, first that Zen 2 retains the same 512KB of L2 cache per core with Zen 2 and second that the processor offers a 16x16MB L3 cache configurations per CPU.Â

This configuration will give AMD’s 64-core Zen 2 EPYC processors up to 256MB of L3 cache, which equates to 4MB per core. With their 1st Generations EPYC 32-core flagship models, AMD offers 16MB of L3 Cache per CPU die, delivering a total of 64MB of L3 Cache, which equates to 2MB of L3 cache per CPU core.Â

The 16x16MB L3 configuration also suggests that each CPU die on AMD’s Zen 2 EPYC processors features two bundles of L3 cache, indicating that the processor will feature a dual CCX configuration within each CPU die, with each CCX featuring four cores each. There are eight CPU dies on AMD’s 64-core EPYC 2 processors, which means that each die features a total of 32MB of L3 cache.Â

Other aspects of this engineering sample seem to indicate that it features a base clock speed of 1.4GHz and a boost clock speed of 2.0GHz, though strangely the system only features 128 threads across two processors, suggesting that SMT has been disabled on the dual socket setup. Low clock speeds are expected from early silicon.Â

Â

While it is possible that SiSoftware has misread the specifications of AMD’s Zen 2 EPYC processors, though the inclusion of such a large L3 cache is undoubtedly possible on 7nm and would give AMD’s processors a performance advantage in specific workloads. L3 cache is something which can be changed on an SKU-by-SKU basis, so AMD’s use of a larger L3 cache is not guaranteed on the company’s Zen 2 based desktop products, especially if their EPYC CPU dies are not utilised on mainstream desktop processors.Â

AMD has not officially confirmed the L3 cache size of their Zen 2 EPYC processors, though this information will likely come to light over the next few months, as AMD’s Second Generation EPYC processors approach their official release.Â

You can join the discussion on AMD’s 2nd Generation EPYC processors featuring a 2x increase in L3 Cache size on the OC3D Forums.Â