Western Digital and Toshiba have reportedly created 128-layer 3D NAND

Western Digital and Toshiba have reportedly created 128-layer 3D NAND

Western Digital’s BiCS NAND is was created thanks to a collaboration between Sandisk, who are now owned by Western Digital, and Toshiba, a move which allowed both companies to develop high speed/capacity 3D flash technology. In simple terms, adding more layers to this type of flash adds more capacity per die, similar to how increasing the number of floors on a building would result in more available rooms/floorspace.Â

Previously, Western Digital’s BiCS NAND was able to offer a total of 96 layers, with the move to 124 layers delivering around 33% more storage per chip. This technology can be used to create higher capacity NAND flash chips, or allow Western Digital to develop smaller chips that offer the same capacities as before, reducing the cost of each chip in the process.

Blocks and Files has reported that Western Digital 128-layer NAND products will start appearing in late 2020, with a production ramp in 2021. In total, Western Digital’s 128-layer BiCS NAND can offer capacities of 512Gb per chip, which translates to 64GB.

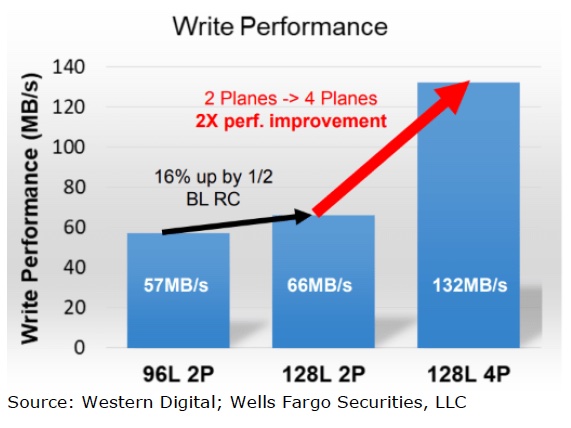

It has also been reported that Western Digital has started using a Circuit under Array (CuA) design to pack logic circuits under the base of their NAND to free up more die area, effectively making their NAND a 23% die shrink. In effect, this is like moving a car park from the outskirts of a large building to a location underneath the structure, conserve land area. Western Digital also reports a boost in write performance thanks to their move from a 2-plane structure to a 4-plane structure, adding more parallelism to their memory, as shown below. Â

Â Â

Â

By decreasing die area usage and offering higher stacks of 3D memory, Western Digital is enabling their memory division to offer more storage capacity per unit of die area, which allows them to reduce the cost/GB of their future memory chips. This will make their memory cheaper to produce in time and increase their production volume (in terms of GB produced). This will, in turn, lead to the production on higher capacity memory chips and reduced NAND pricing.Â

You can join the discussion on Western Digital’s 128-player 3D NAND technology on the OC3D Forums.Â